Brit Chip Company Picks RISC-V For Next-gen Microcontrollers

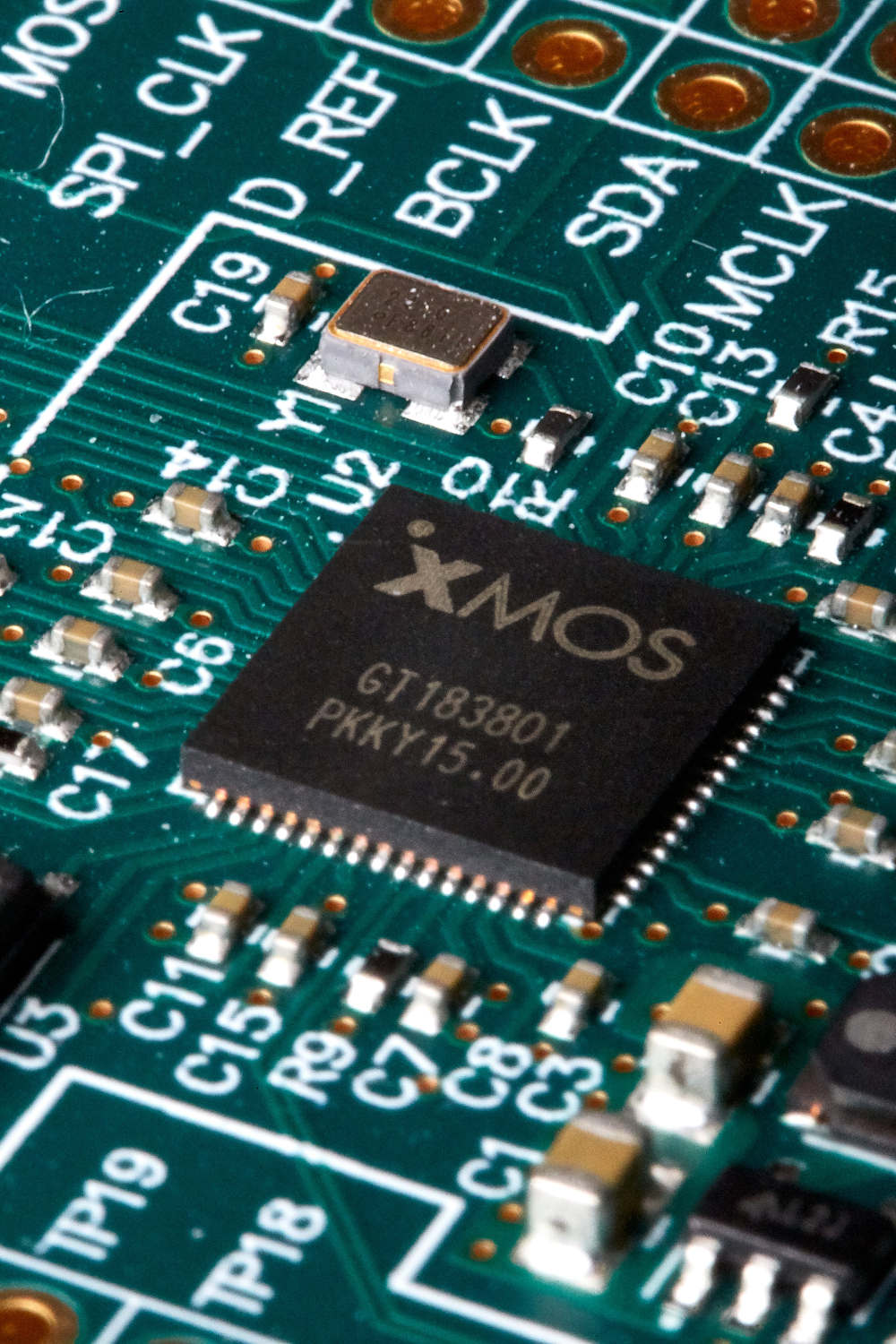

RISC-V Summit British chip company XMOS has revealed its latest xcore high-performance microcontrollers are to be built around the RISC-V open standard instruction set architecture, in the hopes of opening up the silicon to a wider range of embedded system designers.

Unveiled at the RISC-V Summit in San Jose, which starts today, the fourth generation of xcore chips will ditch the proprietary instruction set architecture the company used until now.

This will enable the xcore 400 family to benefit from a broader ecosystem of developer tools and the company also hopes it will appeal to a wider audience of developers and designers.

"We've always been very positively disposed towards open source, and this really is an extension of that philosophy, if you like," XMOS CEO Mark Lippett told The Register.

"So we've always used LLVM compilers and GDB debuggers, for example, but this gives our customers access to a much richer set of tools that that may or may not have been developed with XMOS, and frankly, that's a more capital efficient model for us, because we don't have to develop those things, as there are companies that are focused just on those technologies, and we're very happy to benefit from them, and we think our customers will very much appreciate that as well," he added.

Based at Bristol in the west of England, XMOS is a fabless semiconductor company, but it actually sells the chips directly to customers, unlike fellow Brit chip company Arm, which licenses its designs to others.

As microcontrollers, the xcore chips are used in embedded applications, providing the compute power inside a range of devices from smart TVs to audio kit to network appliances or industrial robotics. Unlike some, XMOS designed its chips around high performance and implementing functions in real-time software rather than adding dedicated hardware modules around the processor cores.

"I'm talking about the sort of flexibility that might previously have only been delivered by something like an FPGA," said Lippett. "So whereas FPGAs use logic cells, we use threads, or in the RISC-V world, harts [hardware threads]." For example, the second generation of xcore chips introduced a Gigabit Ethernet NIC implemented as a software module, he told us.

"In the fourth generation, we'll be supporting the four sort of 'key pillars' of processing if you like: I/O processing, DSP, AI, and control – and using any combination of those four, you can build entire systems just using software modules," he explained.

While the xcore 400 family will execute the RISC-V instruction set, this has effectively been grafted onto the existing architecture to produce the new generation, Lippett claimed, with some minor changes such as increasing the register file size to that implied by the RISC-V instructions.

"Since xcore is a RISC processor with extensions, the mapping of the RISC-V part was, perhaps, easier than you imagine. Instruction encodings needed to change, register file sizes, but that was the bulk of the implementation work," he said.

In those areas where xcore has unique instruction requirements – I/O is controlled directly by instructions – XMOS has used the extensibility of the RISC-V architecture to add its own.

While the xcore 400 architecture is being unveiled at the RISC-V Summit today, the actual chips are not likely to ship until the second half of next year, Lippett said.

However, he declined to reveal which foundry is producing the chips, citing confidentiality, nor what process node they will be manufactured with, saying only that it is not a leading edge node such as 5nm or 7nm.

There will be a family of chips, but all based around a basic tile that comprises two cores, each capable of eight hardware threads. These can scale by adding additional tiles, linked by a high-speed interconnect, and the interconnect also functions as an inter-chip fabric, so that "if you run out of resources on one chip, you can put another chip next to it, join it up using the link technology built into the device, and it will look like a single chip with twice the resources," Lippett told us.

- US chip group: $52b is not enough, we need an extra $30b in federal funding

- Alibaba, Tencent enlisted to help sanction-weary China build RISC-V chips

- Looking for a holiday DIY project? Build your own pen-plotter, for under $15

- Ubuntu continues expanding RISC-V support – now, the $17 Sipeed LicheeRV

"So from a programming model perspective, it scales very, very nicely. And similarly, you don't lose timing determinism, you don't lose any of those things that we rely on to deliver the functions that we deliver," he added.

Lippett said that xcore 400 will be "dropping the operating frequency slightly" compared with the current generation, and "buying back the performance with architectural innovation."

So while the current architecture is clocked at 800MHz and features a 256bit wide dual issue scalar pipeline, xcore 400 will "also focus on getting the power down to a place where it could be in battery applications and wearables and so on," he said.

XMOS said it will be discussing xcore 400 and its adoption of the RISC-V architecture during the RISC-V Summit this week. ®

From Chip War To Cloud War: The Next Frontier In Global Tech Competition

The global chip war, characterized by intense competition among nations and corporations for supremacy in semiconductor ... Read more

The High Stakes Of Tech Regulation: Security Risks And Market Dynamics

The influence of tech giants in the global economy continues to grow, raising crucial questions about how to balance sec... Read more

The Tyranny Of Instagram Interiors: Why It's Time To Break Free From Algorithm-Driven Aesthetics

Instagram has become a dominant force in shaping interior design trends, offering a seemingly endless stream of inspirat... Read more

The Data Crunch In AI: Strategies For Sustainability

Exploring solutions to the imminent exhaustion of internet data for AI training.As the artificial intelligence (AI) indu... Read more

Google Abandons Four-Year Effort To Remove Cookies From Chrome Browser

After four years of dedicated effort, Google has decided to abandon its plan to remove third-party cookies from its Chro... Read more

LinkedIn Embraces AI And Gamification To Drive User Engagement And Revenue

In an effort to tackle slowing revenue growth and enhance user engagement, LinkedIn is turning to artificial intelligenc... Read more